Présentation et parcours

Mes activités de recherche ont été conduites au Laboratoire de Physique de la Matière de l’INSA de Lyon (LPM, UMR CNRS 5511, à présent INL), au Laboratoire de Physique des composants à semi-conducteur (LPCS, UMR CNRS 5531, à présent IMEP) et à l’Université d’Etat de Caroline du Nord (NCSU) entre novembre 1996 et septembre 2001. D’octobre 2001 à septembre 2007, mes activités de recherche ont été conduites au Laboratoire de Matériaux et de Micro-électronique de Provence (L2MP, UMR-CNRS 6137, à présent IM2NP). Depuis octobre 2007, ma recherche s’effectue au Laboratoire d’Electronique, d’Automatique et de Télécommunications (LEAT, UMR-CNRS 6071).

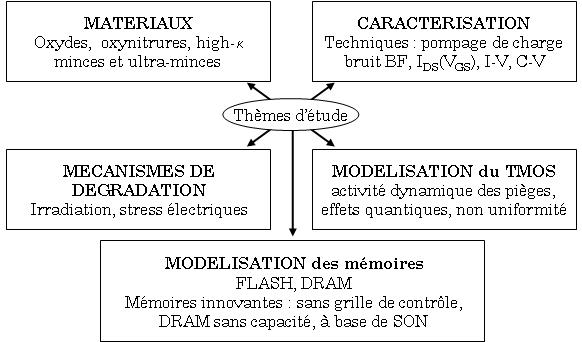

La figure ci-dessus donne une vue synthétique de mes domaines de recherche depuis ma thèse. Initialement mes activités portaient sur la caractérisation électrique des matériaux puis à ma première mutation mes activités se sont portées sur la caractérisation, la modélisation et la simulation du TMOS et des mémoires. Depuis ma deuxième mutation, mes activités portent exclusivement sur la modélisation-simulation du TMOS et des mémoires. Je donne ci-après plus de précision sur ces quatre thématiques.

Thématiques et évolutions

Doctorat et MCF à l’Insa de Lyon (1996-2001)

Mes recherches ont porté sur la caractérisation du transistor MOS à oxynitrure de grille ultra-mince (de 7 nm à 1.8 nm) en fonction de la teneur en azote dans la couche isolante, de son recuit post-fabrication (gaz et température) et de la présence éventuelle d’une couche supplémentaire d’oxynitrure à forte teneur en azote (8 %) dans l’empilement de grille sous la couche de polysilicium. Pour mener à bien cette étude, trois techniques de caractérisation ont été mises en œuvre : les mesures IDS(VGS), de pompage de charge et de bruit basse fréquence (en 1/f). Ces travaux m’ont permis de développer une approche originale de la simulation dynamique du pompage de charge. Ce simulateur a notamment permis de prédire la signature électrique d’un piège unique en pompage de charge 3 niveaux. Cette prédiction a été confirmée par la suite sur des transistors de 50 nm de longueur de grille.

J’ai aussi participé à une campagne de micro-irradiation de transistors MOS sous faisceau X qui permet la création de défauts électriquement actifs localisés sur une surface réduite de l'isolant de grille. La campagne d’irradiations s’est déroulée à l'ESRF de Grenoble en février 1999 et a démontré la faisabilité d’une telle technique d’irradiation. Les résultats obtenus ont montré (en fonction de la dose) que de courtes durées d’irradiation (1 à 3 s) permettent de créer un nombre considérable de défauts électriquement actifs au niveau de la zone irradiée (2 µm²). Nous avons aussi constaté que les zones de claquage de l’isolant étaient différentes des zones irradiées.

Thématiques et évolutions :

MCF et Pr au L2MP (2001 – 2007)

Mes travaux de modélisation des cellules mémoires a nécessité un travail très important sur la modélisation du transistor (effet canal court, ionisation par impact, mobilité, non uniformité du dopage ou de l’épaisseur d’isolant, effets quantiques, dépolarisation du canal…) et de la capacité MOS (poly-désertion, courant tunnel…). Les modèles développés ont permis d’extraire la densité spatiale (entre le substrat et la grille) des charges piégées lors du cyclage de la capacité tunnel de la mémoire EEPROM par le biais de mesures du courant tunnel. Ces modèles couplés à celui du pompage de charge ont été utilisés pour déterminer les caractéristiques des pièges (densité et section efficace de capture) induits par l’utilisation de matériaux isolants de type High-k (HfO2) à partir de mesures CV en fréquence.

Ce travail a été utilisé pour modéliser plusieurs mémoires en commençant par la mémoire Flash à grille flottante. Le logiciel développé à partir de ce modèle a permis de déterminer les caractéristiques des mémoires Flash et de mener des études sur l’optimisation de la géométrie et des signaux de programmation. Ce code a aussi été utilisé pour la simulation du plan mémoire au sein du laboratoire. Ce modèle a ensuite été adapté à la mémoire EEPROM ce qui a permis de définir une méthode d’extraction de la caractéristique IV de la capacité tunnel directement sur la cellule, méthode que nous avons appelé « méthode de grille flottante modifiée ». J’ai aussi travaillé sur la mémoire Flash à nano-cristaux de silicium. Ces boules de silicium remplacent la traditionnelle grille flottante et autorisent un amincissement de l’isolant de grille et une meilleure immunité aux défauts de cet isolant. Les modèles développés ont aussi été mis à profit pour modéliser une mémoire Flash simple poly (donc compatible CMOS) avec transistor annulaire. Là aussi le simulateur a été utilisé pour définir la forme des signaux à appliquer à la cellule pour augmenter son endurance, signaux qui ont été implémentés dans le produit final. J’ai aussi travaillé sur la mémoire DRAM embarquée et sur la mémoire 1TDRAM. Cette mémoire volatile permet de s’affranchir de la réalisation de la traditionnelle capacité de stockage de la DRAM en modulant le potentiel de substrat d’un transistor qui peut être réalisé suivant plusieurs technologies. J’ai travaillé sur la mémoire 1TDRAM bulk qui correspond à un transistor MOS dont le substrat est isolé avec une diode. Ce travail a abouti à la réalisation d’un prototype de 1 kbits.

Pr au LEAT (2007 – 2011)

Mes travaux de recherches au LEAT ont été soutenus par un contrat nano 2012 avec STMicroelectronics Crolles et portent sur la modélisation – simulation de la mémoire 1TDRAM. J’ai travaillé, avec le Pr Philippe LORENZINI, sur le transistor à double grilles indépendants dont la présence ou l’absence de trous accumulés dans le film mince permet de mémoriser l’information 1 ou 0 (fonctionnement en 1TDRAM). Bien que des modèles de ce transistor existent déjà, ils ne prennent pas (et ne peuvent pas) prendre en compte la couche d’accumulation de trous. J’ai donc activement participé à la réalisation d’un simulateur dynamique de cette mémoire qui prend en compte la géométrie et les matériaux utilisés pour le transistor mais aussi les courants de drain, de diode, de génération recombinaison, d’ionisation par impact et de tunnel bande à bande. Les effets de canal court ainsi que les effets quantiques ont aussi été intégrés à notre modèle. Nous avons ainsi pu étudier l’influence des paramètres technologiques sur l’efficacité des phases d’écriture et de rétention et mettre en évidence les paramètres les plus importants.